- 您现在的位置:买卖IC网 > Sheet目录323 > EK-K7-KC705-CES-G-J (Xilinx Inc)KINTEX-7 FPGA KC705 EVAL KIT

�� �

�

�

�Kintex-7� FPGAs� Data� Sheet:� DC� and� AC� Switching� Characteristics�

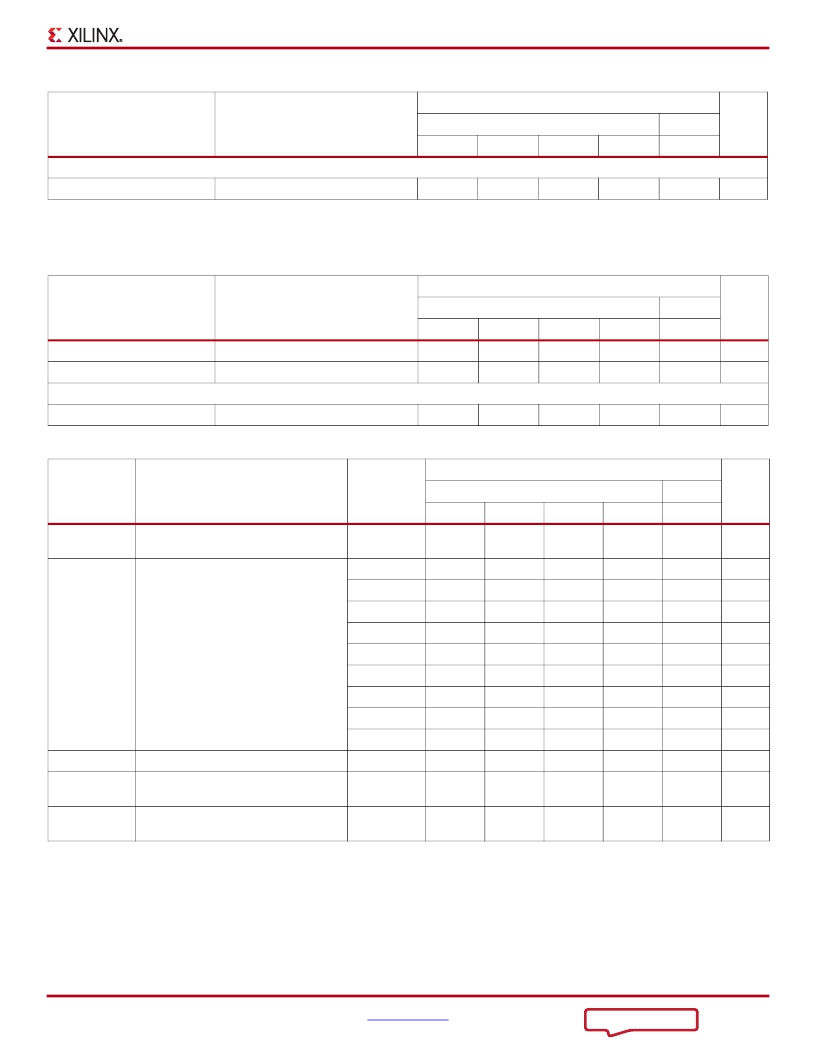

�Table� 36:� Regional� Clock� Buffer� Switching� Characteristics� (BUFR)� (Cont’d)�

�Speed� Grade�

�Symbol�

�Description�

�1.0V�

�0.9V�

�Units�

�-3�

�-2/-2L�

�-1�

�-1M�

�-2L�

�Maximum� Frequency�

�F� MAX_BUFR� (1)�

�Regional� clock� tree� (BUFR)�

�600.00�

�540.00�

�450.00�

�450.00�

�450.00�

�MHz�

�Notes:�

�1.�

�The� maximum� input� frequency� to� the� BUFR� and� BUFMR� is� the� BUFIO� F� MAX� frequency.�

�Table� 37:� Horizontal� Clock� Buffer� Switching� Characteristics� (BUFH)�

�Speed� Grade�

�Symbol�

�Description�

�1.0V�

�0.9V�

�Units�

�-3�

�-2/-2L�

�-1�

�-1M�

�-2L�

�T� BHCKO_O�

�BUFH� delay� from� I� to� O�

�0.10�

�0.11�

�0.13�

�0.13�

�0.12�

�ns�

�T� BHCCK_CE� /T� BHCKC_CE�

�CE� pin� Setup� and� Hold�

�0.20/0.16� 0.23/0.20� 0.38/0.21� 0.38/0.79� 0.28/0.09�

�ns�

�Maximum� Frequency�

�F� MAX_BUFH�

�Horizontal� clock� buffer� (BUFH)�

�741.00�

�710.00�

�625.00�

�625.00�

�560.00�

�MHz�

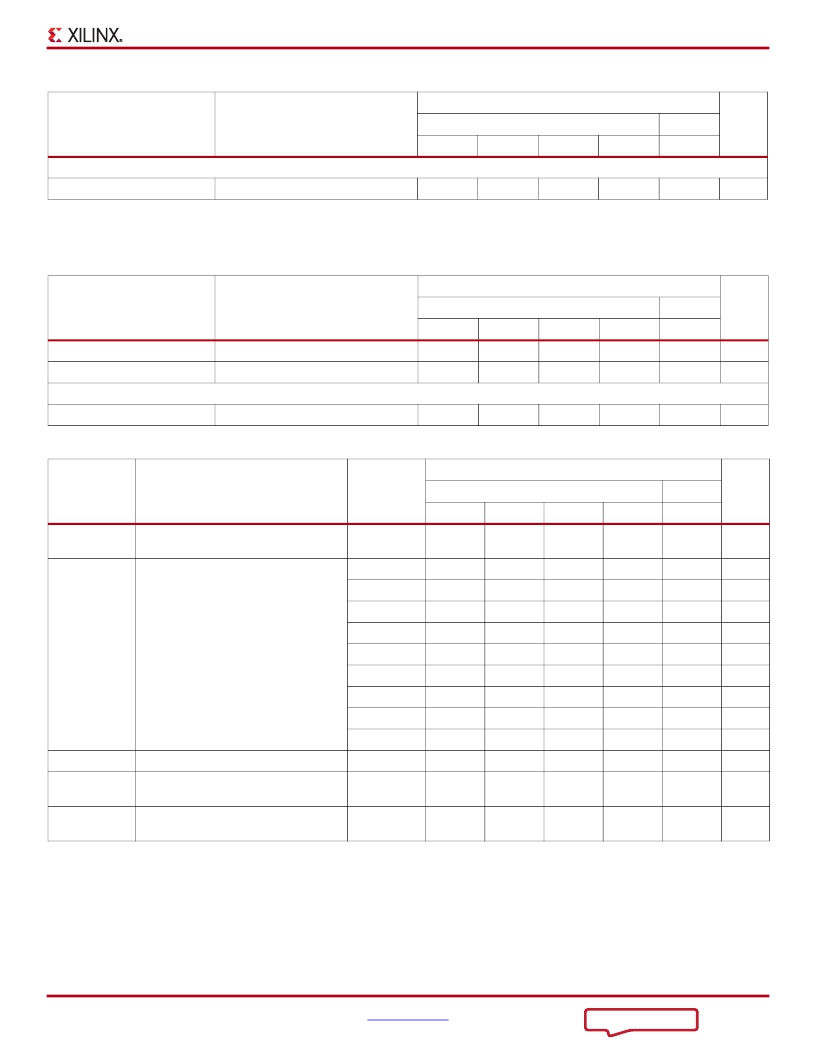

�Table� 38:� Duty� Cycle� Distortion� and� Clock-Tree� Skew�

�Speed� Grade�

�Symbol�

�Description�

�Device�

�-3�

�-2/-2L�

�1.0V�

�-1�

�-1M�

�0.9V�

�-2L�

�Units�

�T� DCD_CLK�

�T� CKSKEW�

�T� DCD_BUFIO�

�T� BUFIOSKEW�

�T� DCD_BUFR�

�Global� Clock� Tree� Duty� Cycle�

�Distortion� (1)�

�Global� Clock� Tree� Skew� (2)�

�I/O� clock� tree� duty� cycle� distortion�

�I/O� clock� tree� skew� across� one� clock�

�region�

�Regional� clock� tree� duty� cycle�

�distortion�

�All�

�XC7K70T�

�XC7K160T�

�XC7K325T�

�XC7K355T�

�XC7K410T�

�XC7K420T�

�XC7K480T�

�XQ7K325T�

�XQ7K410T�

�All�

�All�

�All�

�0.20�

�0.29�

�0.42�

�0.59�

�0.45�

�0.60�

�0.60�

�0.60�

�N/A�

�N/A�

�0.12�

�0.02�

�0.15�

�0.20�

�0.40�

�0.53�

�0.74�

�0.57�

�0.74�

�0.74�

�0.74�

�0.74�

�0.74�

�0.12�

�0.02�

�0.15�

�0.20�

�0.40�

�0.57�

�0.79�

�0.59�

�0.79�

�0.79�

�0.79�

�0.79�

�0.79�

�0.12�

�0.02�

�0.15�

�0.20�

�N/A�

�N/A�

�N/A�

�N/A�

�N/A�

�N/A�

�N/A�

�0.79�

�0.79�

�0.12�

�0.02�

�0.15�

�0.25�

�0.47�

�0.59�

�0.91�

�0.69�

�0.91�

�0.91�

�0.91�

�0.91�

�0.91�

�0.12�

�0.03�

�0.15�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�Notes:�

�1.�

�2.�

�These� parameters� represent� the� worst-case� duty� cycle� distortion� observable� at� the� I/O� flip� flops.� For� all� I/O� standards,� IBIS� can� be� used� to�

�calculate� any� additional� duty� cycle� distortion� that� might� be� caused� by� asymmetrical� rise/fall� times.�

�The� T� CKSKEW� value� represents� the� worst-case� clock-tree� skew� observable� between� sequential� I/O� elements.� Significantly� less� clock-tree�

�skew� exists� for� I/O� registers� that� are� close� to� each� other� and� fed� by� the� same� or� adjacent� clock-tree� branches.� Use� the� Xilinx� Timing� Analyzer�

�tools� to� evaluate� clock� skew� specific� to� your� application.�

�DS182� (v2.8)� March� 4,� 2014�

�Product� Specification�

���39�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EK-S6-SP601-G

KIT EVAL SPARTAN 6 SP601

EK-S6-SP605-G

KIT EVAL SPARTAN 6 SP605

EK-V6-ML631-G-J

VIRTEX-6 HXT FPGA ML631 EVAL KIT

EK-V7-VC707-CES-G

VIRTEX-7 VC707 EVAL KIT

EK-Z7-ZC702-CES-G

ZYNQ-7000 EPP ZC702 EVAL KIT

EL1848IYZ-T7

IC LED DRIVR WHITE BCKLGT 8-MSOP

EL7156CSZ

IC DRIVER PIN 40MHZ 3STATE 8SOIC

EL7158ISZ

IC DVR PIN 40MHZ 3STATE 8-SOIC

相关代理商/技术参数

EK-K7-KC705-G

制造商:Xilinx 功能描述:KINTEX-7 FPGA KC705 EVALUATION KIT 制造商:Xilinx 功能描述:KINTEX-7 FPGA KC705 EVALUATION KIT - Boxed Product (Development Kits) 制造商:Xilinx 功能描述:KINTEX-7 FPGA KC705 EVAL KIT

EK-K7-KC705-G-J

制造商:Xilinx 功能描述:KINTEX-7 FPGA KC705 EVAL KIT

EKK8011

制造商:未知厂家 制造商全称:未知厂家 功能描述:USB + PS/2 keyboard controller

EKK8011AB

制造商:EMC 制造商全称:ELAN Microelectronics Corp 功能描述:USB & PS/2 Keyboard Encoder

EKK8301

制造商:未知厂家 制造商全称:未知厂家 功能描述:PS/2 keyboard controller

EKK-EVALBOT

功能描述:开发板和工具包 - ARM Keil Stellaris Eval Robot

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

EKK-LM3S1968

功能描述:开发板和工具包 - ARM Stellaris Eval Kit w/ ARM/Keil Tools RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

EKK-LM3S1968

制造商:Texas Instruments 功能描述:LM3S1968 MCU Eval Kit w/ Keil RealView M